I.T.I.S. “E. FERMI”

Francavilla Fontana (BR)

Esercitazione n°3

ALUNNO Giodice Dario CLASSE 4 SEZ A/inf

LABORATORIO Elettronica Prof. Pietro De Paolis/ Guido Lupo

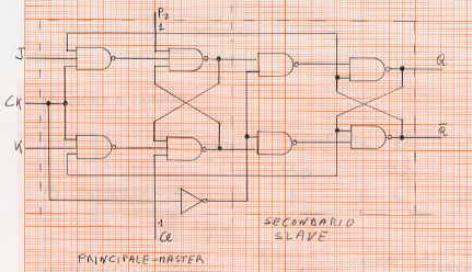

Obbiettivo

dell’esercitazione: Rilevazione sperimentale della tabella di verità di

un Flip - Flop

Master Slave con otto porte nand e una not

Strumentazione

utilizzata:

- breadboard,

- due integrati 74LS10

- un integrato 74LS04

- un integrato 74LS00

- una resistenza da 125 Ω(ohm)

- led di colore rosso

- generatore da 5v (volt)

- cavi di conduzione.

Rappresentazione

grafica dello schema:

(Rappresentazione di un flip flop master slave)

(Rappresentazione di un flip flop master slave)

(Fotografie del circuito realizzato)

Svolgimento dalla

prova:

Nell’esercitazione numero tre, lo scopo è di ricavare sperimentalmente la tabella di verità di un flip-flop master slave per vedere se coincide perfettamente con le nozioni teoriche.

In un flip flop master-slave le operazioni svolte seguono un ritmo temporale che viene “dettato” dall’impulso di clock:

![]()

Il nostro gruppo ha deciso di costruire questo flip flop utilizzando 8 porte logiche nand e 1 not.

Il flip flop master slave risolve il problema della trasparenza; infatti grazie all’ingresso di clock il circuito commuta durante il fronte di salita dell’impulso di clock. Come si può notare nella rappresentazione grafica del circuito, in esso è presente anche una not. Il not serve appunto a far si che lo slave resti bloccato durante il fronte positivo dell’impulso di clock. Quando il clock ritorna a 0, il secondo stadio (cioè lo slave) viene abilitato. Come già detto,il master slave risolve il problema della trasparenza.Infatti le uscite commutano non solo quando commutano gli ingressi ma anche quando è terminato l’intero impulso di clock.

Il flip flop di tipo master slave è un circuito diviso in due parti uno detto master ed uno detto slave. Il master memorizza i valori che assumono gli ingressi durante il fronte di salita del clock,mentre lo slave adegua l'uscita allo stato degli ingressi durante il fronte di discesa del clock; Affinché possa avvenire la commutazione del circuito occorre un intero impulso di clock.

La tabella di verita che avremmo dovuto ottenere è la seguente:

|

CK |

J |

K |

Qn+1 |

|

0 |

X |

X |

Qn |

|

_ é ù

_ |

0 |

0 |

Qn |

|

_ é ù _ |

0 |

1 |

0 |

|

_ é ù _ |

1 |

0 |

1 |

|

_ é ù _ |

1 |

1 |

Qn |

Conclusioni: Dopo aver montato accuratamente il circuito, stando attenti a non

commettere errori, abbiamo verificato la veridicità della tabella soprastante. Purtroppo

però non è stato possibile ottenere la tabella

di verità corretta perché molto probabilmente alcuni integrati non erano ben

funzionanti. E’ per questo motivo,quindi, che non è possibile affermare la

riuscita dell’esercitazione nonostante il circuito è stato montato bene.

Giodice

Dario

4°A/inf